### NBER WORKING PAPER SERIES

### HOW FAST ARE SEMICONDUCTOR PRICES FALLING?

David M. Byrne Stephen D. Oliner Daniel E. Sichel

Working Paper 21074 http://www.nber.org/papers/w21074

NATIONAL BUREAU OF ECONOMIC RESEARCH 1050 Massachusetts Avenue Cambridge, MA 02138 April 2015

We received helpful comments from Ana Aizcorbe, Ernie Berndt, Erwin Diewert, Ken Flamm, Charlie Gilbert, Robert Hill, Kevin Krewell, Catherine Mann, Chris Nosko, Unni Pillai, Paul Thomas, Neil Thompson, Vincent Russo and other analysts in the Producer Price Index program at the Bureau of Labor Statistics, as well as seminar participants at the Federal Reserve Bank of Boston, the 2013 IARIW/UNSW Conference and Workshop, the NBER weekly productivity seminar, the 2014 CRIW/NBER Summer Institute, and the Wellesley Economics Department brown-bag series. The views expressed herein are those of the authors and do not necessarily reflect the views of the National Bureau of Economic Research or the views of the other institutions with which we are affiliated.

NBER working papers are circulated for discussion and comment purposes. They have not been peerreviewed or been subject to the review by the NBER Board of Directors that accompanies official NBER publications.

© 2015 by David M. Byrne, Stephen D. Oliner, and Daniel E. Sichel. All rights reserved. Short sections of text, not to exceed two paragraphs, may be quoted without explicit permission provided that full credit, including © notice, is given to the source.

How Fast are Semiconductor Prices Falling? David M. Byrne, Stephen D. Oliner, and Daniel E. Sichel NBER Working Paper No. 21074 April 2015 JEL No. E01,E31,E66,L16,L63,N12,N72,O33

### ABSTRACT

The Producer Price Index (PPI) for the United States suggests that semiconductor prices have barely been falling in recent years, a dramatic contrast from the rapid declines reported from the mid-1980s to the early 2000s. This slowdown in the rate of decline is puzzling in light of evidence that the performance" of microprocessor units (MPUs) has continued to improve at a rapid pace. Roughly coincident with to slower price declines in the PPI, Intel — the leading producer of MPUs — substantially changed its pricing behavior for these chips. As a result of this change, we argue that the matched-model methodology used in the PPI for MPUs likely started to be biased in the mid-2000s and that hedonic indexes can provide a more accurate measure of price change since then. Our preferred hedonic index of MPU prices tracks the PPI closely through 2004. However, from 2004 to 2008, our preferred index fell faster than the PPI, and from 2008 to 2013 the gap widened further, with our preferred index falling at an average annual rate of 43 percent, while the PPI declined at only an 8 percent rate. Given that MPUs currently represent about half of U.S. shipments of semiconductors, this difference has important implications for gauging the rate of innovation in the semiconductor sector.

David M. Byrne Federal Reserve Board 20th & Constitution Ave., NW Washington, DC 20551 david.m.byrne@frb.gov

Stephen D. Oliner American Enterprise Institute 1150 17th St., NW Washington, DC 20036 and UCLA Ziman Center for Real Estate stephen.oliner@aei.org Daniel E. Sichel Department of Economics Wellesley College 106 Central Street Wellesley, MA 02481 and NBER dsichel@wellesley.edu

### **1. Introduction**

How fast are semiconductor prices falling? Data from the Producer Price Index (PPI) published by the U.S. Bureau of Labor Statistics indicate that prices of microprocessor units (MPUs) have barely been falling in recent years. This very slow rate of price decline stands in sharp contrast to the rapid declines in MPU prices reported from the mid-1980s up to the early 2000s and the exceptionally rapid declines in the latter half of the 1990s. If accurate, the apparent slowdown in MPU price declines in recent years would be troubling, given the long-run relationship between rates of price decline of semiconductors and the pace of innovation in that sector.<sup>1</sup>

A stalling out of innovation in this sector likely would have broader implications for the economy, as semiconductors are an important general-purpose technology lying behind advances of the digital revolution, including machine learning, robotics, big data, and massive connectivity.<sup>2</sup> Given this connection, adverse developments in the semiconductor sector could damp the growth potential of the overall economy.<sup>3</sup> On the other hand, if technological progress and attendant price declines were to continue at a rapid pace, powerful incentives would be in place for continued development and diffusion of new applications of this general-purpose technology. Such applications could both enhance the economy's growth potential and push forward the ongoing automation that has generated concerns about job displacement.<sup>4</sup>

The apparent slowdown in the rate of price decline is puzzling given evidence that the performance of MPUs continued to improve at a rapid pace after the mid-2000s. The key to resolving the puzzle may reside in another development in the semiconductor industry. Roughly

<sup>&</sup>lt;sup>1</sup> See Aizcorbe, Oliner, and Sichel (2008) for a discussion of the relationship between price change and innovation for semiconductors.

<sup>&</sup>lt;sup>2</sup> Brynjolfsson and McAfee (2014) and Baily, Manyika, and Gupta (2013) highlight key innovations in many sectors of the economy.

<sup>&</sup>lt;sup>3</sup> For discussions of the sources of a possible slowdown in the economy's potential growth rate, see Cowen (2011), Fernald (2014), Gordon (2012, 2014a, and 2014b), Hall (2014), and Jorgenson, Ho, and Samuels (2014).

<sup>&</sup>lt;sup>4</sup> For a recent discussion of these employment issues, see Hamilton Project (2015) for the transcript of a wideranging Policy Forum.

coincident with the shift to a slower pace of price decline in the PPI, Intel — the leading MPU producer — dramatically changed its pricing behavior. Prior to the mid-2000s, Intel generally lowered the list prices of existing chips to remain competitive with newly-introduced chips on a price-performance basis. However, after the mid-2000s, Intel shifted to a new paradigm in which it largely kept the list prices of existing chips unchanged.

This change in Intel's behavior could resolve the puzzling disconnect between continuing improvements in MPU performance and the shift to slower price declines. Namely, we argue that the matched-model methodology used by BLS is not well suited to capturing price trends in a pricing regime like the one that has prevailed since the mid-2000s. In such a pricing regime, if performance is improving over time, then matched-model price indexes for MPUs such as the PPI likely are biased. We argue that a specific hedonic index — one based on prices for newly-introduced models — is better suited to capturing price trends in these circumstances and develop new hedonic indexes for quality-adjusted prices using price data for Intel MPUs from 2000 to 2013.

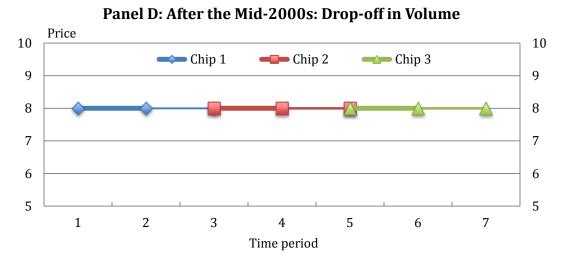

Our preferred index of MPU prices tracks the PPI closely from 2000 to 2004. However, from 2004 to 2008 — roughly the period of transition to Intel's new pricing regime — our preferred index fell faster than the PPI. And from 2008 to 2013, the gap widened further, with our preferred index falling at an average annual rate of 43 percent, while the PPI declined at only an 8 percent rate.

An important innovation in the paper is that the hedonic regressions utilize measures of MPU performance on typical tasks for computer users rather than technical variables capturing physical characteristics (such as feature size) and engineering specifications (such as clock speed). Performance measures provide a superior control for quality change when constructing

- 2 -

price indexes for MPUs because they gauge the actual output obtained by a user rather than the input characteristics used to produce that output. Moreover, with rapid changes in MPU architecture in recent years, identifying the correct set of technical characteristics (and likely changes in that set) could be challenging.

To gauge whether our measure of user performance matters empirically, we also estimate parallel hedonic regressions with technical characteristics as the controls for chip quality. The price indexes generated by the two approaches are strikingly different after 2004. The declines in the indexes based on technical characteristics slowed sharply from that point forward, much like the PPI. After 2004, clock speed — which had been highly correlated with user performance — stopped rising in response to problems with heat generation, but Intel continued to boost performance in other ways. The hedonic regressions we estimated with technical characteristics evidently cannot capture the ongoing gains in performance, which translates into slower declines in constant-quality prices. This result highlights the importance of using direct measures of performance when estimating hedonic price regressions.

This paper focuses on MPUs rather than a broader set of semiconductor products, a choice we made for several reasons.<sup>5</sup> First, MPUs are a large segment of the semiconductor sector; in 2014, they represented about half of U.S. shipments (the scope of the PPI). Second, price series for MPUs extend back to the mid-1980s, allowing for comparisons of price trends over time. Given that price trends in this sector often are used to infer rates of technical progress, this historical comparability is important. Finally, we believe that developments in

<sup>&</sup>lt;sup>5</sup> Among all MPUs, this paper analyzes prices of the MPUs used in desktop personal computers (PCs), for which data are the most readily available. In other work, we are developing indexes for MPUs going into servers, the types of machines that would support cloud computing in server farms and other processor-intensive applications. In addition, Dan Sichel's undergraduate thesis student, Sophie (Liyang) Sun (2014) developed price indexes for MPUs used in laptop computers.

MPU technology likely provide a rough guide to developments in other parts of the semiconductor sector, such as the chips that are used in smartphones and tablets.<sup>6</sup>

Our work on MPU prices builds on important earlier research. Much prior work on semiconductor prices relied on technical characteristics of the chips to control for quality. Notable studies that have used this approach to construct hedonic price indexes for semiconductors (or computing equipment that embeds these chips) include Cole et al. (1986), Grimm (1998), and Flamm (2007).

Although the technical characteristics used in these studies are correlated with performance, they may not fully capture the capabilities of the processor for end users. For this reason, Triplett (1989) and Berndt and Griliches (1993) called for analysis of computer prices with controls for more refined measures of performance.<sup>7</sup> In this vein, Chwelos (2000 and 2003) constructed hedonic price indexes for PCs with controls for the results of a suite of benchmark performance tests.<sup>8</sup>

An alternative approach has been to measure semiconductor prices with matched-model indexes. Aizcorbe, Corrado, and Doms (2003) found that under certain circumstances (highly granular data on model prices and high-frequency observations), a matched-model index may produce similar results to a hedonic index. Such highly granular data were used by the Federal Reserve Board for its MPU price index through 2006, which was constructed as a matched-model index. The source data used by the Fed were discontinued after 2006. However, even if

<sup>&</sup>lt;sup>6</sup> The market for chips going into smartphones and tablets is changing rapidly, and it is challenging to obtain consistent time series on prices and performance. That being said, the production processes and technologies are similar enough to those for MPUs that developments in MPUs likely provide at least a rough gauge of developments in these other types of chips.

<sup>&</sup>lt;sup>7</sup> See pages 147 and 91, respectively.

<sup>&</sup>lt;sup>8</sup> In addition, Holdway (2001) examined unit value MPU price indexes using benchmark test scores as a measure of quality-adjusted units of computing power. Grimm (1998) developed specifications that controlled for millions of instructions per second (MIPS); this measure of performance, however, has limited ability to account for differences across MPUs in the translation of instructions into program execution.

those data were still available, the issues explored in this paper suggest that the matched-model approach would be problematic for more recent years.

This paper extends the existing literature in two main ways. First, we develop hedonic price indexes for MPUs that control for quality with performance measures based on typical tasks performed by end users. Second, we use these hedonic price indexes to assess the possibility that the PPI has been understating the price declines for MPUs.

The next section highlights the puzzle raised by the very slow rate of decline in the PPI during recent years at the same time that the engineering frontier for MPUs continued to move out rapidly. This section also discusses the change in the pricing pattern of Intel MPUs that occurred in the mid-2000s. Section 3 presents our argument that hedonic price indexes are likely to better capture price trends than are matched-model indexes (such as the PPI) since that change. Section 4 reviews our data, which cover the period from 2000 to 2013. In section 5, we describe the hedonic regressions used to obtain measures of quality-adjusted prices. Section 6 presents our results, and section 7 concludes.

### 2. The Puzzle

As noted, the PPI for MPUs has fallen very slowly in recent years. This section explores the plausibility of this extreme slowdown from two different perspectives. The first perspective is whether the slowdown meshes with the trends in technological advance for MPU chips. The second perspective focuses on the changes that occurred in Intel's pricing patterns for MPUs, developments that, as we show below, have important implications for price index measurement.

*Technology cycles and chip performance.*<sup>9</sup> The standard definition of a semiconductor technology cycle is the amount of time required to achieve a 30 percent reduction in the width of the smallest feature on a chip. Because chips are rectangular, a 30 percent reduction in both the horizontal and vertical directions implies about a 50 percent reduction (0.7\*0.7) in the area required for the smallest chip component. As documented in Byrne, Oliner, and Sichel (2013), the semiconductor industry has achieved massive reductions in scaling over time. Indeed, the area occupied by a chip component in 2012 was roughly 200,000 times smaller than in 1969.

There is a broad consensus that the pace of technical advance in the semiconductor industry sped up in the mid-1990s, a development first brought to the attention of economists by Jorgenson (2001). Table 1 reports the average length of the semiconductor technology cycle (as defined above) for various periods. For the industry as a whole, the technology cycle averaged three years until 1993 and then dropped to about two years from 1993 to 2012. Within the later period, the scaling advances were especially rapid from 1993 to 2003 and a bit slower after 2003. Even so, the average cycle since 2003 has remained substantially shorter than the three-year cycle in effect before the 1990s. For Intel's MPU chips, there has been no pullback at all from the two-year cycle. The upshot is that the cycles in semiconductor technology — a key driver of quality improvement in IT products — have remained rapid.<sup>10</sup>

While the pace of miniaturization has been sustained, semiconductor producers have changed the approach used to translate these engineering gains into faster performance. Historically, each new generation of technology in semiconductors allowed for an increase in the

<sup>&</sup>lt;sup>9</sup> The text in this section draws heavily on material in Byrne, Oliner, and Sichel (2013). In addition, table 1 comes directly from that paper.

<sup>&</sup>lt;sup>10</sup> These continuous increases in chip density are the force behind Moore's Law, which states that the number of components on leading-edge chips will double every two years. Moore's original formulation (Moore, 1965) pegged the doubling time at only one year, but in 1975 he revised the period to be two years based on the actual experience to that point (Intel Corporation, 2005). For a discussion of the outlook for Moore's Law, see Bauer, Veira, and Weig (2013).

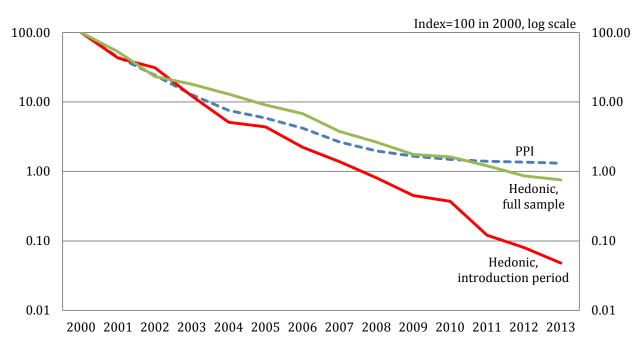

number of basic calculations performed per second (clock speed) for a given chip design. However, as speed continued to increase, dissipating the generated heat became problematic. In response, Intel shifted away in the early to mid-2000s from increases in clock speed and boosted performance instead by placing multiple copies of the core architecture on each chip — a change enabled by smaller feature size — and by improving the design of those cores.<sup>11</sup>

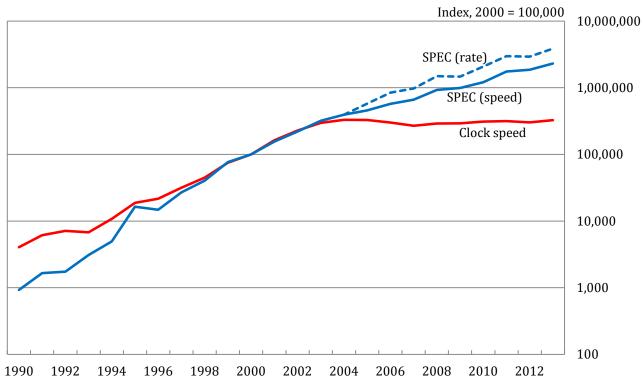

How did this strategy shift affect the rate of increase in performance for end users? For the period through 2008, Pillai (2013) addressed this question with performance scores from the Standard Performance Evaluation Corporation (SPEC).<sup>12</sup> These scores are based on standard tasks designed to reflect the needs of computer users. Figure 1 extends Pillai's analysis through 2013, plotting average SPEC performance measures for MPUs introduced each year.<sup>13</sup> Starting in 2004, the figure includes a second SPEC performance measure (the "rate" score) that incorporates more fully the performance gain from using multiple cores than does the standard ("speed") measure.<sup>14</sup>

Figure 1 confirms Pillai's finding that MPU performance gains cooled around 2001 from the extraordinary pace in the 1990s, though the rate of advance has, nonetheless, remained substantial through 2013. Using the SPEC rate measure that accounts more completely for the effects of parallel processing, SPEC performance rose about 32 percent per year on average from 2000 to 2013, down from the 60 percent rate of improvement from 1990 to 2000 and the 36 percent pace over the earlier 1971-90 period (not shown). The figure also plots clock speed for

<sup>&</sup>lt;sup>11</sup> See Shenoy and Daniel (2006). Also, Hennessy and Patterson (2012) document that increases in clock speed stalled out during this period (figure 1.11, p. 24).

<sup>&</sup>lt;sup>12</sup> SPEC is a non-profit corporation that establishes performance benchmark tests for computing equipment and publishes test results submitted by member organizations.

<sup>&</sup>lt;sup>13</sup> The data through 1999 were kindly provided by Unni Pillai. We linked these data with SPEC performance results for 1999-2013 that we obtained directly from SPEC. We accessed the SPEC data on May 20, 2014 and used the benchmark suites SPEC® CPU2006 and SPEC® CPU2000. The SPEC score for each year is the average over the Intel desktop MPU chips introduced in that year. Details are provided in section 4 and in appendix A.

<sup>&</sup>lt;sup>14</sup> See section 4 for further discussion of these alternative SPEC tests.

Intel desktop MPUs, highlighting that performance continued to improve even as clock speed stalled out in the early to mid-2000s.<sup>15</sup>

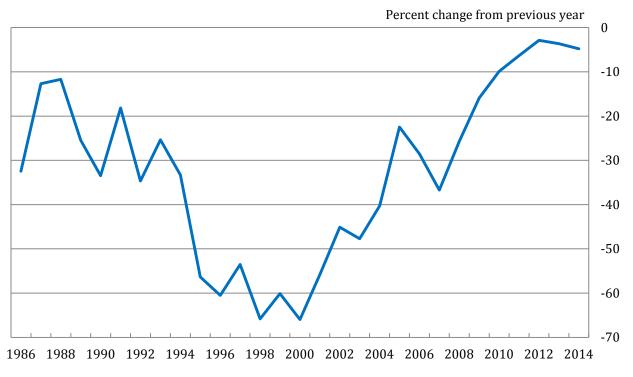

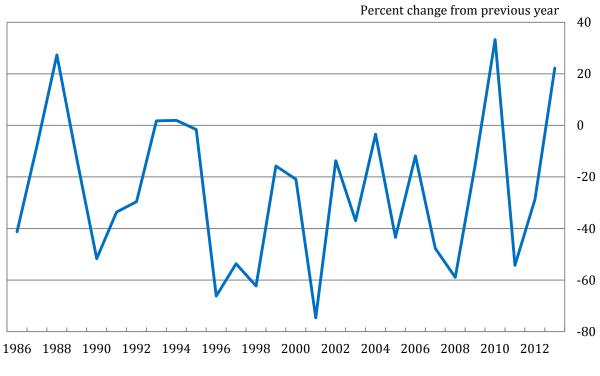

Historically, improvements in the engineering frontier have translated into steep declines in MPU prices. Figure 2 shows the annual price declines back to 1986, splicing together estimates from Grimm (1998) through 1992, the Federal Reserve Board for 1993-97, and the PPI for later years. Over this period, MPU prices fell at an average rate of nearly 30 percent per year, with especially sharp drops in the second half of the 1990s. However, reported price declines have slowed dramatically over the past several years. Indeed, the declines in each year since 2010 were smaller than in any prior year back to 1986, breaking the link with the continued engineering improvements. Perhaps the cost of achieving these engineering advances has accelerated in recent years. If that were the case, we might expect to see a similar price pattern for other types of semiconductor chips. No such pattern, though, is evident for memory chips (DRAMs).<sup>16</sup> As shown in figure 3, DRAM prices have been quite volatile from year to year, with no clear trend toward slower declines. At least for DRAMs, then, the translation of the engineering frontier to prices does not appear to have changed.

All in all, the shift to much slower price declines for microprocessors in the PPI is a puzzle in light of the continued substantial improvements on the engineering front. We next consider the possibility that changes in the properties of Intel's posted prices after 2006 could have distorted the measurement of price trends in the PPI.

<sup>&</sup>lt;sup>15</sup> During the first half of the 1990s, performance also increased more rapidly than did clock speed. Hennessy and Patterson (2012) discuss this pattern; see the note to their figure 1.11.

<sup>&</sup>lt;sup>16</sup> The most important driver of DRAM performance is the size of the components on the chip, which has continued to shrink rapidly, as discussed above. See Flamm (1993) for a discussion of characteristics of DRAM chips.

*Intel's pricing behavior and market position.* Between 2003 and 2006, the properties of Intel's posted prices for MPU chips changed dramatically.<sup>17</sup> Prior to 2003, the price of a specific Intel MPU model tended to drop fairly rapidly in the year or two following its introduction, especially once a new, higher performance model became available. By 2006, this pattern had completely changed; the posted price of a specific model tended to remain constant, even after a new, higher performance model became available at a similar price.

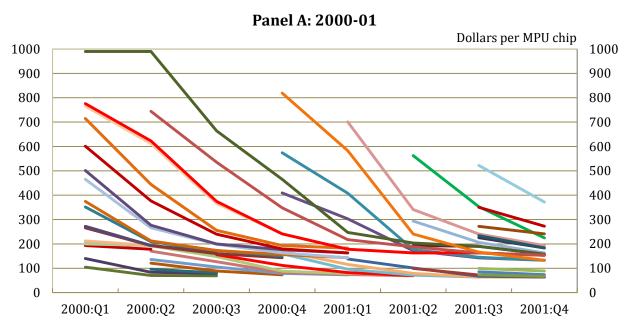

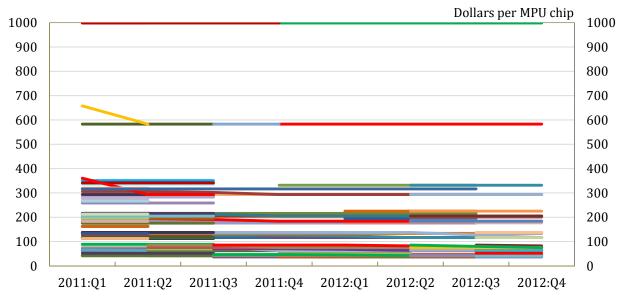

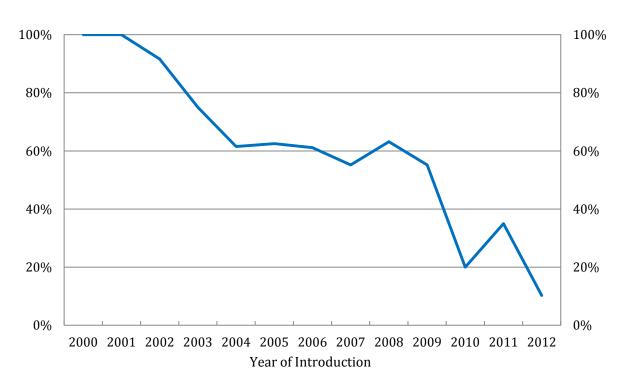

Figure 4 illustrates this shift in pricing behavior. The upper panel shows Intel wholesale list prices for all desktop models during 2000-01, while the lower panel shows the analogous list prices for all desktop models during 2011-12. The difference between the two panels is stark. In the early period, prices fell steeply over a model's lifecycle. However, by 2011-12, the price paths are flat or nearly so, with only a few instances of sizable price declines. Figure 5 summarizes this change in life-cycle pricing over the entire 2000-12 period by showing the share of all Intel desktop MPU models introduced in each year that experienced a price decline within four quarters of introduction.<sup>18</sup> As can be seen, every model introduced in 2000 and 2001 had at least one such price cut. But the share then dropped to about 60 percent for the 2004 to 2009 cohorts and took another leg down thereafter, falling to roughly 10 percent for the 2012 cohort.

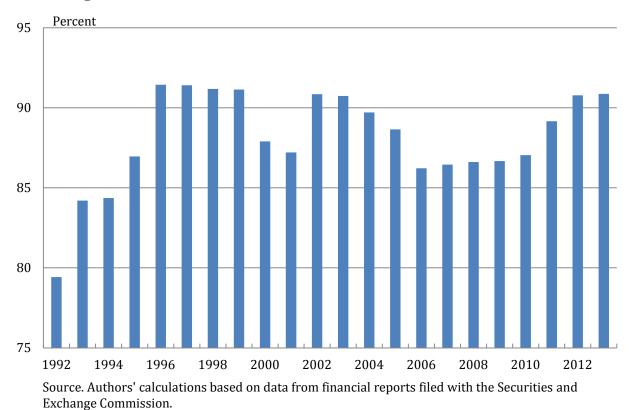

This shift took place against the backdrop of a changing competitive environment vis-avis AMD, Intel's primary challenger in the MPU market. Figure 6 plots Intel's annual revenue from all products (not only MPUs) as a share of Intel's and AMD's combined revenue. Over this 20-year period, Intel's revenue share ranged from just under 80 percent to slightly above 90 percent. In 2002 and 2003, Intel's share stood at the top of this range but then eroded

<sup>&</sup>lt;sup>17</sup> While the BLS does not indicate which companies' prices are included in the PPI for MPUs, it is only reasonable to assume that Intel is included given its dominant market position. Moreover, it appears that BLS has been making at least some use of Intel's posted prices for MPUs (see Holdway, 2001).

<sup>&</sup>lt;sup>18</sup> The price data in the figure are described in section 4.

significantly through 2006. Nosko (2010) also documented this share erosion, noting that from 2002 to 2006, AMD "consistently released products whose price/performance characteristics were similar to or beat Intel's" (p. 8). Documents from legal actions against Intel for alleged antitrust violations (see, for example, State of New York v. Intel Corporation, 2009) also provide evidence that Intel was concerned about its losses of market share to AMD during this period.

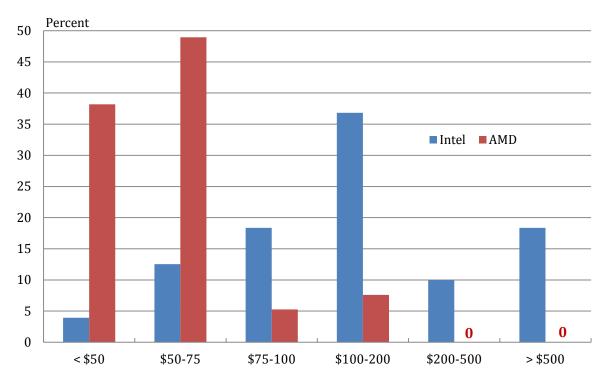

However, in 2006, Intel began to turn the corner by offering new MPUs that dominated those sold by AMD (see Nosko, 2010, for details) and subsequently pulled ahead of AMD in a decisive way, consistent with the recovery in Intel's overall revenue share. By 2013, Intel's dominance had reached the point that AMD effectively had been relegated to the bottom end of the MPU market. Indeed, as shown in figure 7, AMD received more than 85 percent of its MPU revenue from chips that sold for less than \$75, the low-end part of the market where Intel derived only about 15 percent of its revenue. Conversely, Intel received almost 30 percent of its MPU revenue from chips that sold for \$200 or more, a segment in which AMD earned no revenue.<sup>19</sup>

This evidence indicates that Intel has enhanced its position in the MPU market since 2006. With less competition from AMD, Intel has greater scope to manage its price structure.<sup>20</sup> By keeping list prices essentially fixed over a chip's life cycle, Intel may be attempting to extract more revenue from price-insensitive buyers while offering discounts on a case-by-case basis to other customers. Such price discrimination could reduce the information content of its posted list prices, potentially biasing the quality-adjusted indexes generated from these prices. The next

<sup>&</sup>lt;sup>19</sup> Figure 7 slightly overstates the market separation between Intel and AMD for the following reason. The source data used to construct the figure show the average selling prices for distinct product families (Intel's Core i5 Duo, for example) rather than prices for individual chips. Within each product family, there is some amount of unobserved price variation. The average selling price for AMD's most expensive product family, the FX-8, was less than \$200 in 2013, but two chips in this family (the FX-9590 and the FX-9370) were priced between \$200 and \$500 at introduction in July 2013 (see <a href="http://en.wikipedia.org/wiki/List\_of\_AMD\_FX\_microprocessors">http://en.wikipedia.org/wiki/List\_of\_AMD\_FX\_microprocessors</a>). These isolated cases do not affect the general point that Intel dominates the high end of the MPU market.

<sup>&</sup>lt;sup>20</sup> For models of pricing and innovation behavior in the MPU industry, see Aizcorbe and Kortum (2005), Nosko (2010), and Pillai (2013).

section investigates the properties of matched-model and hedonic indexes in the post-2006 pricing environment.

### 3. Constructing MPU Price Indexes

As noted, the changes in the pattern of Intel's posted MPU prices raise important questions for price measurement. Can a matched-model index correctly capture price trends given Intel's new pricing regime? If not, what approach to price measurement is likely to deliver estimates that are most robust to possible measurement error in prices? Finally, in an environment with rapid gains in MPU performance and changes in chip architecture, what are the best ways to measure quality change for MPUs?

In this section, we investigate these questions and make the case that — given the new pricing regime for MPUs that emerged in the mid-2000s — hedonic indexes are preferable to matched-model indexes. In addition, we argue that, given possible measurement error and current limitations on data availability, hedonic regressions that rely only on prices in the period of a model's introduction are likely to be more robust than hedonic regressions that include prices over a chip's entire life cycle. We also argue that hedonic indexes using actual measures of performance have important advantages over those using variables capturing physical characteristics of MPUs.

*Matched-model or hedonic?* To fix ideas, we briefly describe the matched-model and hedonic approaches to price measurement (see Aizcorbe, 2014, for a recent, in-depth treatment of this topic). Matched-model indexes control for quality change between two periods, say period 0 and period 1, by averaging price changes for models that were in the market in both periods. The underlying idea is to measure "pure" (or quality-adjusted) price change for products whose quality did not change because they were in the market in both periods 0 and 1.

- 11 -

Hedonic price indexes identify "pure" price change by explicitly controlling for quality change with measures of product characteristics or performance. The hedonic approach regresses prices on these measures, with the price change left after controlling for quality taken to be the quality-adjusted price change. Many alternative specifications have been proposed for hedonic regressions. Perhaps the simplest is to include time dummy variables (time fixed effects) in the hedonic regression and to read off quality-adjusted price change from the coefficients on the time dummies. (We discuss in section 5 our preferred specification for the new price indexes in this paper.)

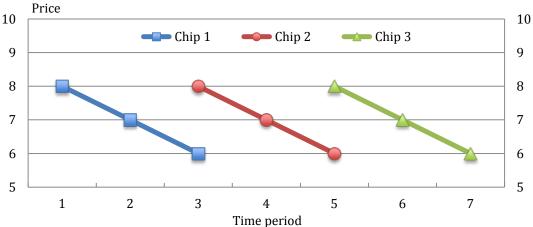

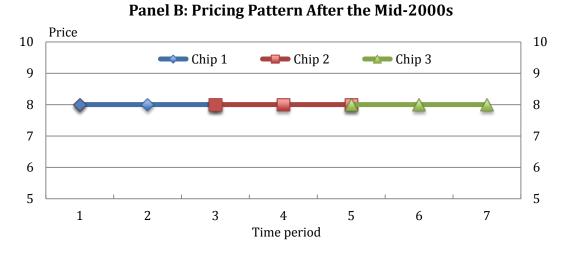

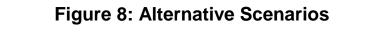

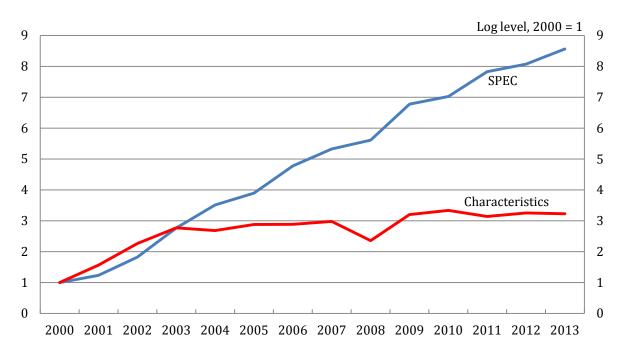

To illustrate why we prefer hedonic over matched-model indexes for MPUs, we use stylized examples of Intel's pricing behavior to highlight the implications of the shift in behavior. Panel A of figure 8 illustrates the pricing pattern for Intel MPUs prior to the mid-2000s in which the price of each MPU model falls as it ages; this panel is a stylized version of the actual price cascade for 2000-01 shown previously. When a new, higher-quality model is introduced, the price of the old model falls so that price *per unit of quality* is at least roughly equalized across models. In this case, the gap between model prices in periods when two models are in the market would represent the value of improved quality, and a matched-model index would correctly adjust for this quality change.

Panel B shows a scenario in which prices of incumbent models do not fall when new, higher-quality models are introduced — a stylized version of the actual price cascade we presented for 2011-12. Given the upward trend in chip quality, price per unit of quality in panel B is falling as new models are introduced. However, a matched-model index would indicate that quality-adjusted prices are constant because the price of each model stays the same as it ages. Thus, a matched-model index would give a biased read of trends in quality-adjusted prices.

- 12 -

In contrast, a hedonic index that used appropriate measures of quality would correctly capture price trends even in the scenario in Panel B. In that scenario, prices are not changing, but the quality measure in the hedonic regression would account for the improvement in priceperformance ratios when new models are introduced, and a hedonic index would show a downtrend in quality-adjusted prices reflecting the decline in price per unit of quality.

These scenarios illustrate why we believe that matched-model indexes will generate biased price trends in the period following the shift in Intel's pricing behavior, and why we believe that hedonic indexes are more likely to correctly capture price trends for MPUs.

*Introduction-period or full-sample hedonic regressions?* A natural starting point would be to assume that hedonic regressions should be estimated using all available data. However, under certain circumstances, a full-sample regression can lead to biased estimates of price change. For example, in the 1980s some researchers constructed price indexes for mainframe computers using only introduction-period prices for each model. This choice was made because of concerns that available IBM list prices for older models might not be actual transaction prices (see Cole et al., 1986).

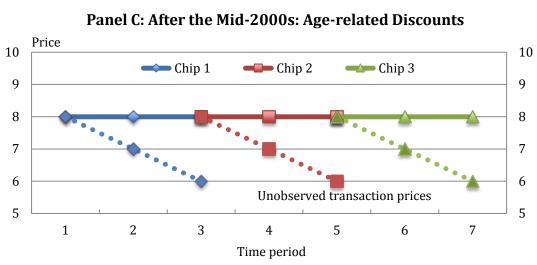

We believe a similar concern may apply to MPUs. To explain why, we consider two possible explanations for what lies behind the pricing pattern adopted by Intel in the mid-2000s. Panel C of figure 8 shows a stylized scenario in which prices of older models are measured with error. Specifically, posted list prices in this scenario do not represent true transactions prices because Intel offers "age-related discounts" to selected purchasers as models age. In this scenario, new models enter the market at the same list price that exiting models leave the market, just as in panel B. We now add the dashed lines, which show actual transaction prices. These

- 13 -

lines slope downward, as progressively larger discounts are offered on older models as newer, higher performance models become available.

In the age-related discounting scenario, a full-sample hedonic index based on observable *posted* prices would go astray because the posted prices are measured with error. The actual transaction prices of each model are falling over time but a full-sample hedonic index would not account for this measurement error, leading to biased estimates of quality-adjusted price change.

In contrast, the introduction-period hedonic index could correctly capture trends in quality-adjusted prices if age-related discounts were offered as in panel C.<sup>21</sup> In particular, the introduction-period hedonic would omit observations in which prices were measured with error, and the performance variables in the regression would control for improvements in quality in successive periods.

Panel D highlights another scenario ("Drop-off in volume") that also could create challenges for a full-sample hedonic index. In this scenario, posted prices do not change, but in contrast to panel C, we assume they represent actual transaction prices. With this pricing assumption, the quantity purchased of a model drops off as it ages and faces competition from newer, more powerful models with lower prices per unit of quality. The solid, heavier line represents the early, high-quantity part of each model's life cycle and the thinner line represents the later part when sales have dropped. If model-level data on shipments or sales were available, a shipments- or sales-weighted index would account for the declining importance of the older model. However, model-level quantity data are not readily available. Accordingly, we (and other researchers) are forced to consider price indexes that put equal weight on every observation.

<sup>&</sup>lt;sup>21</sup> The introduction-period index would capture price trends even if list prices at the time of introduction do not represent actual transactions prices provided that discounts at the time of introduction do not vary systematically over time or across models.

In the scenario illustrated in panel D, an unweighted full-sample hedonic index would put too much weight on price observations for which there were few transactions. In contrast, an unweighted introduction-period hedonic index likely would do a better job of capturing the trend in quality-adjusted prices. By focusing on prices at the beginning of each model's life-cycle, a regression that applies equal weights to all observations avoids over-weighting models whose quantities have dropped off.

For the reasons described here, we emphasize introduction-period hedonic indexes, although we also report full-sample indexes. Our preference does not reflect a belief that introduction-period indexes are inherently better, but rather the view that introduction-period indexes are likely to be more robust to the data limitations that hamper efforts to estimate recent trends in quality-adjusted MPU prices. In particular, we believe that an introduction-period hedonic will be more robust to measurement error in list prices (the age-related discount scenario) and to a lack of model-level shipments data that prevents the use of weighted regressions (the drop-off in volume scenario).

*Performance measures or physical characteristics in hedonic regressions?* A longrecognized challenge facing hedonic methods has been the choice of variables to include in the regression to control for quality. The typical approach has been to include measures of key physical characteristics of each model, in the belief that these characteristics will serve as a proxy for what purchasers value. This approach has raised concerns in the past, and researchers have called for the inclusion of actual performance measures rather than physical characteristics (see Triplett, 1989, and Berndt and Griliches, 1993). The underlying logic behind using performance measures is to focus on the output received by users rather than the input characteristics used to generate that output. For many products, measures of performance are unavailable so there is little choice but to use characteristics. For MPUs, however, measures of performance — specifically for the types of tasks actually undertaken by users — are available as described above. Moreover, specifying an appropriate hedonic regression and finding suitable data can be difficult for a rapidly evolving product, and using directly measured performance helps to address this problem.

Accordingly, in this paper, we develop hedonic indexes with performance measures from SPEC that avoid the difficulties entailed in trying to capture quality for MPUs with rapidly changing architecture by identifying relevant physical characteristics. Our preferred performance metrics are described in detail in the next section.

### 4. Data

*Prices and SPEC scores.* Our MPU prices are collected from publicly available Intel price lists for the period from 1999 to 2013.<sup>22</sup> Intel announces wholesale list prices several times a year for MPUs sold in multiples of 1,000. Unlike single units sold in retail channels, these "trays" of MPUs do not include a cooling system and carry a shorter warranty. Models are identified by family (for example, Core i7, Pentium, Core 2 Duo), model ID (for example, i7-4960X), and selected technical characteristics (for example, amount of cache memory or clock speed). We merged these price lists to create price data at a quarterly frequency. We restrict our attention to the 373 MPU models for desktop computer systems introduced between 2000 and 2013.

To measure the relative quality of different chips we use the performance scores from SPEC that were mentioned in section 2. (These benchmark tests are described in detail in

<sup>&</sup>lt;sup>22</sup> Price lists for the period from April 1999 to December 2006 were collected from an archived version of a website devoted to computer hardware. Price lists for later dates were obtained directly from Intel's website. On dates when both sources were available, we confirmed that the website prices matched Intel price lists.

appendix A.) Briefly, SPEC scores evaluate performance of an MPU on individual tasks that rely heavily on integer computation (such as word processing) and on tasks that rely heavily on floating point computation (such as speech recognition). Scores for individual tasks are measured in seconds, although SPEC rescales these scores so that higher scores indicate better performance and the units are no longer in seconds. SPEC provides an overall score both for integer and for floating-point computation, which are calculated as geometric means of scores for 12 integer computation tasks and 17 floating-point computation tasks, respectively. To construct a single measure of performance, we take the geometric mean of the overall scores for integer and floating-point tasks.<sup>23</sup>

SPEC scores are widely used to compare the performance of alternative MPUs or computers and also are used as a standard by computer engineers.<sup>24</sup> For example, Hennessy and Patterson (2012) — the standard text on computer design and architecture — notes that "One of the most successful attempts to create standardized benchmark application suites has been the SPEC (Standard Performance Evaluation Corporation) …" (p. 38). This textbook relies on SPEC scores to measure the growth in processor performance in recent decades.<sup>25</sup>

SPEC benchmarks provide several ways to measure MPU performance. The performance of a single task is measured by the "speed" score and the simultaneous performance of multiple tasks is measured by the "rate" score. The "speed" and "rate" scores differ in their use of parallel processing, an important consideration after the introduction of multi-core MPUs in the mid-2000s. In the "speed" test, a single task may be broken into component calculations to be run on different processing cores on the MPU. In the "rate" test, multiple instances of the

<sup>&</sup>lt;sup>23</sup> Although the integer and floating-point scores could be included as separate variables in the hedonic regressions described below, little would be gained relative to the equal-weighted geometric mean, as the correlation between the two scores is greater than 0.98.

<sup>&</sup>lt;sup>24</sup> One of our employers uses SPEC scores in making decisions about purchases of computing equipment.

<sup>&</sup>lt;sup>25</sup> See figure 1.1 on page 3.

same task may be run simultaneously to more fully exploit the potential of the chip. We use the "speed" score as our base case, but the results using the "rate" score (available from the authors) are very similar.

*Sample selection*. We matched 184 MPU models from our price data, or 49 percent, to at least one performance score published by SPEC. An important question is whether this selection on the availability of SPEC scores could bias our results. Table 2 provides information on this point, showing a range of chip characteristics both for chips with SPEC scores and for those without scores.<sup>26</sup> As shown in Panel A of the table, average entry prices for chips with SPEC scores are considerably higher than for chips without SPEC scores. Perhaps not surprising given the difference in average prices, chips with SPEC scores tend to have technical features associated with higher performance. Clock speed is somewhat greater for chips with SPEC scores; the shift to multicore architecture occurred more quickly; and the amount of power used by the chip (thermal design power<sup>27</sup>) is greater. For the most part, these difference in the final characteristic shown in the panel — the size of the smallest feature on the chip (lithography).

For our purposes, the essential issue is whether price trends differ across the samples of chips with and without SPEC scores. To examine this question, we construct matched-model indexes using the PPI methodology (labeled PPI-like) for both samples. As shown in Panel B of the table, over the full period from 2000 to 2013, the average rate of decline in these PPI-like price indexes is very similar across the chips with and without SPEC scores (29 percent versus 26 percent, respectively). The two sets of chips also display similar price trends within the

<sup>&</sup>lt;sup>26</sup> The information on characteristics is collected from Intel's product information database (<u>http://ark.intel.com</u>).

<sup>&</sup>lt;sup>27</sup> Thermal design power (TDP) measures the amount of heat generated when running typical software for the chip. The amount of heat generated (measured in watts) is closely related to the MPU's power consumption.

shorter time periods shown in the table. The similarity of the price trends suggests that our results are not biased by the absence of SPEC scores for some chip models.

*Representativeness of our sample relative to the PPI.* A second important question is how well price trends in our sample track those in the PPI. Our sample is for Intel desktop chips, while the scope of the PPI includes desktop chips from other manufacturers (notably including AMD), as well as chips for servers and laptops. As can be seen in Panel B, our PPI-like indexes for Intel desktop chips and the PPI for all MPUs display very similar price trends. Accordingly, we are comfortable using our results for Intel desktop chips to draw inferences about the performance of the PPI.

### 5. Specification of the Hedonic Regressions

To fix ideas, we first describe a dummy-variable hedonic specification:

$$\ln(P_{i,t}) = \alpha + \sum_{k} \beta_k X_{k,i,t} + \sum_{t} \delta_t D_{i,t} + \varepsilon_{i,t}$$

(1)

where  $P_{i,t}$  is the price of chip *i* in period *t*,  $X_{k,i,t}$  is the value of characteristic *k* for chip *i* in period *t* (measured in logs or levels, as appropriate),  $D_{i,t \in Y}$  is a vector of time dummy variables (fixed effects) that equals 1 if chip *i* is observed in period *t* and zero otherwise, and  $\varepsilon_{i,t}$  is an error term.

A potential shortcoming of equation 1, highlighted by Pakes (2003) and Erickson and Pakes (2011), is that the coefficients on the characteristic or performance variables are constrained to remain constant over the full sample period. One response to that concern is to run a cross-section regression for every time period and then to use results from those regressions to build up a price index.<sup>28</sup> Such an approach is appealing because it provides maximum flexibility for estimated coefficients to change over time and allows the results to be

<sup>&</sup>lt;sup>28</sup> See Aizcorbe's (2014) discussion and the references there.

used in price index formulas. However, our sample size is too small to run reliable cross-section hedonic regressions for every quarter or even every year.

As a compromise, we focus on adjacent-period (in our case, adjacent-year) hedonic regressions.<sup>29</sup> Specifically, we estimate the following regression for each two-year overlapping period:

$$\ln(P_{i,t}) = \alpha + \sum_{k} \beta_{k} X_{k,i,t} + \delta D_{2} + \varepsilon_{i,t} \qquad (2)$$

where  $P_{i,t}$  is the price of chip *i* in year *t*. We measure  $P_{i,t}$  as the average of the observed prices of chip *i* within the year.<sup>30</sup> The dummy variable  $D_2$  equals 1 if the price observation is in the second year of the two-year overlapping period and 0 otherwise. To construct a price index from this sequence of regressions, we spliced together the percent changes implied by the estimated coefficients on the  $D_2$  variables. In our main results, we rely on the SPEC variable to capture the performance of each MPU as experienced by users, so that  $\sum_k \beta_k X_{k,i,t}$  reduces to  $\beta \ln(SPEC_{i,t})$ .

As noted in the previous section, SPEC updated its suite of performance tests in 2006. We use the older (SPEC 2000) benchmarks for the adjacent-year regressions through 2005-06 and the newer (SPEC 2006) benchmarks for the adjacent-year regressions beginning with 2006-07.

As a comparison, we also estimate equation 2 with a set of chip characteristics on the right-hand side instead of the SPEC variable. This alternative regression represents the usual approach to hedonic specification in the literature and allows us to gauge the effect on estimated price trends of controlling directly for performance. The characteristics included in the regression are those shown in table 2 — clock speed (in gigahertz), number of cores, maximum

<sup>&</sup>lt;sup>29</sup> See Triplett (2006) for a discussion of adjacent-period hedonic regressions.

<sup>&</sup>lt;sup>30</sup> We also estimated regressions at the quarterly frequency for each two-year period and included a time trend spanning the eight quarters of data included in each regression. That alternative yielded price trends similar to those reported here.

thermal design power (in watts), and lithography size (in nanometers) — plus cache memory (in megabytes), a dummy for whether the chip has a separate graphics processing unit, and the number of threads.<sup>31</sup> We use the natural log of clock speed, thermal design power, lithography size, and cache memory; the number of cores and number of threads enter the regression in levels.

# 6. Results

Table 3 shows estimates of equation 2 using SPEC performance for the overlapping two-year periods during 2000-06, and table 4 shows estimates for 2006-13. The upper panel in each table presents estimates that rely only on prices in each MPU model's introduction period, while the lower panel presents estimates based on the full sample of price observations. The coefficient on the second-year dummy variable in each adjacent-year regression measures the rate of change in quality-adjusted MPU prices from the first year to the second.

Overall, the regressions explain much of the variation in MPU prices. The adjusted  $R^2$  averages close to 0.50 across the full set of regressions shown in tables 3 and 4.

Although Pakes (2003) cautions against providing structural interpretations of the coefficients, we note that the coefficients on SPEC performance are uniformly positive and significant at the 5 percent level. These coefficients indicate that higher performing MPU models sell for higher prices and suggest that the performance measure captures an important element of the quality differences across MPU models.

Analogous tables for the regressions that replace SPEC performance with chip characteristics are provided in appendix C. These regressions fit the data well, with an average adjusted  $R^2$  of about 0.75. Some of the estimated coefficients are in line with expectations. In

<sup>&</sup>lt;sup>31</sup> MPUs can perform multiple threads—sequences of related program instructions—either by employing multiple cores or by sharing resources on an individual core. Thus, additional threads provide a form of parallel processing.

particular, the coefficients on clock speed, number of threads, and cache memory are generally positive and significant, with no instances of significant negative coefficients. In contrast, the significant coefficients on thermal design power, number of cores, lithography, and the graphics processor dummy change sign at least once. In addition, the significant coefficients on the graphics processor dummy are generally negative. Overall, these regressions exhibit the interpretational issues that often attend hedonic regressions estimated with a vector of product characteristics.<sup>32</sup>

To construct annual price indexes from the SPEC and characteristics regressions, we set the 2000 value of the index to 100, and then move the index forward year by year with the implied percent change from each adjacent-year regression. For example, to calculate the percent change from 2000 to 2001, we exponentiate the coefficient on the year dummy in the 2000-01 regression.<sup>33</sup> We then do the same for the 2001-02 regression, and so on.

We summarize our results in table 5 and figure 9. The table reports average rates of price change over 2000-04, 2004-08, and 2008-13 from six different measures: the hedonic index based on SPEC performance and introduction-period prices (our preferred index), three other hedonic indexes including those using chip characteristics, the MPU price index constructed by

<sup>&</sup>lt;sup>32</sup> For completeness, we also estimated a version of the hedonic regression that included both SPEC performance and chip characteristics as controls for quality. The results were not crisp, as might be expected given the inclusion of both a summary measure of performance and chip features that influence the summary measure. In particular, the coefficient on SPEC performance was positive and significant in less than half of the regressions and insignificant in the rest. The coefficients on the characteristics, though broadly similar to the characteristics-only regression, displayed more frequent instances of significant changes in sign.

<sup>&</sup>lt;sup>33</sup> Because the exponential function is nonlinear, the translation from the natural log of prices to price levels requires an adjustment in order to be unbiased. We apply the standard adjustment based on the estimated variance of the regression error; see Aizcorbe (2014) for details. This adjustment had very little effect on estimated price trends over 2000-04, but over 2004-08 and 2008-13 it slowed the estimated annual rate of price decline by as much as 10 percentage points relative to the unadjusted estimates.

the Federal Reserve Board, and the PPI.<sup>34</sup> The figure plots the levels of the PPI and the two hedonic indexes based on SPEC performance.

From 2000 to 2004, all of the indexes show very rapid declines in MPU prices. As discussed in section 3, with Intel's ubiquitous downward re-pricing of existing chips before the mid-2000s, all of the price indexes—both matched model and hedonic—would be expected to capture the downward trend in quality-adjusted prices. This expectation is borne out by our results. As shown in table 5, all of the MPU price indexes fell at an average annual rate of 39 percent or more over 2000-04. In addition, the rate of decline in the PPI (and the Fed's index) is very similar to that of our preferred hedonic index.

However, the trends in the indexes diverge after 2004. Although our preferred hedonic index fell somewhat less rapidly after 2004 than before, the decline in the PPI slowed much more sharply. Indeed, the PPI fell at an average annual rate of only 8 percent from 2008 to 2013 and barely declined at all in 2012 and 2013. For the reasons highlighted earlier in the paper, we believe that this divergence points to likely bias in the PPI for MPUs and suggests that the PPI could be providing a deeply misleading picture of price trends for MPUs in recent years.<sup>35</sup>

The full-sample hedonic index based on SPEC performance declined less rapidly than the introduction-period index in each period, with the largest difference occurring after 2008. As indicated by the analysis in section 3, the wider gap after the mid-2000s is what would be expected under the "age-related discounting" and "drop-off in volume" scenarios if Intel were keeping posted prices for older models fixed to a greater degree than previously. Because

<sup>&</sup>lt;sup>34</sup> The Federal Reserve series is a matched-model index from 1992 to 2006 linked to an introduction-period hedonic index after 2006. The hedonic index is constructed from an earlier version of the empirical work presented here.

<sup>35</sup> In a closely related study, Sun (2014) estimated hedonic regressions for MPUs used in laptops. Because SPEC scores were not available for a wide enough set of laptop chips, Sun used a variety of other performance benchmarks in the regressions. She found that prices for laptop MPUs trended down at a 20 to 30 percent average annual pace over past ten years, depending on the regression specification. The rate of price decline slowed after 2010, though not to the extent shown by the PPI.

discounts from posted prices are unobservable, the full-sample index will understate price declines to the extent that Intel is discounting older models; this bias will be larger than when posted prices were more flexible. Moreover, to the extent that Intel is allowing priceperformance ratios on older models to rise above those for new models, sales of the older models likely are falling off more substantially than when posted prices fell over a chip's life cycle. Given that we do not have model-level shipments data, the index based on the unweighted fullsample index would overweight the older models whose prices are not changing. Under either scenario (or a combination of them), the full-sample hedonic index will understate the rate of price decline, supporting our preference for the introduction-period index.<sup>36</sup>

The post-2004 slowing in estimated price declines is much more pronounced in the regressions that use chip characteristics than in those using SPEC performance. As shown in table 5, during 2004-08 and 2008-13, the price indexes obtained from the characteristics-based regressions fell at average annual rates ranging from only 1 percent to 21 percent, a far slower rate of decline than in the corresponding SPEC-based indexes.

The wide gap stems from the post-2004 divergence between the continued performance gains indicated by SPEC scores and the flat path for chip quality implied by the characteristics regression (which we demonstrate below). With no quality improvement, the characteristics regression "thinks" that constant-quality prices are no longer falling more rapidly than observed list prices.

<sup>&</sup>lt;sup>36</sup>As a robustness check for the introduction-period SPEC regression, we estimated an alternative version that included not only chip prices in the quarter of introduction but also prices in the three quarters following the chip's introduction. The price index obtained from this regression fell at a (bias-adjusted) annual rate of 38 percent, 34 percent, and 39 percent, respectively, over 2000-04, 2004-08, and 2008-13. Thus, MPU price declines are estimated to have remained rapid whether we use only the introduction-period price or broaden the sample to include prices observed within a year of introduction.

To measure the implied change in chip quality over time, recall from equation 2 that the effect of quality on the log of observed chip price in the adjacent-year regression is  $\sum_k \beta_k X_{k,l,t}$ . Letting  $t_1$  and  $t_2$  denote the first and second of the two adjacent years, the average value of the quality effect for the chips that appear in the regression in  $t_1$  is  $\sum_k \beta_k \overline{X}_{k,t_1}$ , with an analogous expression for  $t_2$ . Thus, the change in the quality effect from  $t_1$  to  $t_2$  is  $\sum_k \beta_k (\overline{X}_{k,t_2} - \overline{X}_{k,t_1})$ .<sup>37</sup> When SPEC performance is used as the sole control for chip quality, this expression reduces to  $\beta(\overline{X}_{t_2} - \overline{X}_{t_1})$ , where X is  $\ln(SPEC)$ . It is important to note that  $\sum_k \beta_k (\overline{X}_{k,t_2} - \overline{X}_{k,t_1})$  measures the effect of quality change on prices, not the pure change in quality itself. However, on the reasonable assumption that higher quality is associated on average with higher chip prices, the sign of  $\sum_k \beta_k (\overline{X}_{k,t_2} - \overline{X}_{k,t_1})$  indicates whether chip quality is improving, worsening, or remaining unchanged, which is sufficient for our purpose.

Figure 10 shows the time series for the price effect of chip quality, measured from each adjacent-year regression as  $\sum_k \beta_k (\bar{X}_{k,t_2} - \bar{X}_{k,t_1})$ , with each year-pair then linked together to form the time series. The  $\beta$  coefficients and the average chip characteristics are both taken from the introduction-period version of the regressions, and thus represent the price effect of quality at the frontier. As can be seen, the SPEC-based series rises every year, implying a sustained increase in chip quality; this result is consistent with the direct measure of SPEC performance that was shown previously in figure 1. In contrast, the series based on chip characteristics in figure 10 only edges up on net after 2003, implying little effect on prices of the improvement in chip quality from that year forward, punctuated by a sizable decline in 2008. Interestingly, the characteristics-based series in figure 10 bears a striking resemblance to the series for clock speed

<sup>&</sup>lt;sup>37</sup> Aizcorbe (2006) also measures the price effect of changes in chip quality. Although her method involves taking the difference between the changes in observed prices and quality-adjusted prices, algebraically this is very close to what we do.

in figure 1. Thus, even though the characteristics-based regression includes seven MPU characteristics, clock speed exerts a powerful influence on the implied measure of chip quality in the regression.

These results raise questions about the constant-quality MPU price indexes obtained from the regressions that control for quality with chip characteristics. To view those indexes as credible, one must accept either that the quality of MPU chips was essentially stagnant for the decade after 2003 or that the market placed no value on rising performance over that decade. The second condition is implausible on its face, while the first implies that the upward march in chip quality indicated by SPEC ratings — the industry standard for performance measurement is spectacularly wrong. The much more likely conclusion, in our view, is that chip performance has continued to improve and that constant-quality MPU prices have remained on a steep downtrend.

### 7. Conclusion

After falling rapidly through the mid-2000s, the PPI for MPUs has declined very slowly by historical standards in recent years. Such a slowdown is puzzling given evidence of ongoing rapid advances in semiconductor technology. To reconcile these observations, this paper demonstrates that the matched-model procedure used for the PPI for MPUs likely is inappropriate in the pricing regime that Intel — the dominant manufacturer — adopted in the mid-2000s. We argue that a hedonic approach based on introduction-period prices is the preferred way to measure quality-adjusted MPU prices in the current pricing environment. We implement this hedonic approach with an MPU performance measure that addresses

longstanding concerns in the literature about the use of product characteristics to proxy for performance.

The results from our preferred hedonic price index indicate that quality-adjusted MPU prices continued to fall rapidly after the mid-2000s, contrary to the picture from the PPI. Our results have important implications for understanding the rate of technical progress in the semiconductor sector and, arguably, for the broader debate about the pace of innovation and its implications in the U.S. economy. Notably, concerns that the semiconductor sector has begun to fade as an engine of growth appear to be unwarranted. Rather, these results suggest continued rapid advances in technologies enabled by semiconductors.

That said, it is important to highlight that our results have limited direct implications for the measurement of real GDP or output per hour. Semiconductors mostly are intermediate inputs and so are not counted directly in GDP. Imports and exports are the exception, but trade quantities are small enough that, even if our preferred price indexes for MPUs were adopted, measures of real GDP growth would change by only a small amount.

As a final point, we note that our results raise a new puzzle. In recent years, the price index for computing equipment in the National Income and Product Accounts has fallen quite slowly by historical standards. If MPU prices have, in fact, continued to decline rapidly, why have prices for computers — which rely on MPUs for their performance — not followed suit? We believe there is a reasonable chance that the official price indexes for computers have been measured with error, reflecting in part the challenge of identifying the relevant and likely changing set of physical characteristics used to measure quality. The end-user performance measure employed in this paper could help break this knot for computer prices, and we are investigating this possibility in further work.

- 27 -

# References

Aizcorbe, Ana, "Why Did Semiconductor Price Indexes Fall So Fast in the 1990s? A Decomposition," *Economic Inquiry*, 44(3), 485-96, 2006.

A Practical Guide to Price Index and Hedonic Techniques, Oxford University Press, 2014.

\_\_\_\_\_\_, Carol Corrado, and Mark Doms, "When Do Matched-Model and Hedonic Techniques Yield Similar Measures?" Federal Reserve Bank of San Francisco Working Paper No. 2003-14, 2003. <u>http://www.frbsf.org/economic-research/files/wp03-14bk.pdf</u>

\_\_\_\_\_, and Samuel Kortum, "Moore's Law and the Semiconductor Industry: A Vintage Model," *Scandinavian Journal of Economics*, 107(4), 603–30, 2005.

, Stephen D. Oliner, and Daniel E. Sichel, "Shifting Trends in Semiconductor Prices and the Pace of Technological Progress," *Business Economics*, 43(3), 23–39, 2008.

Baily, Martin Neil, James Manyika, and Shalabh Gupta, "U.S. Productivity Growth: An Optimistic Perspective," *International Productivity Monitor*, 25, 3-12, 2013. <u>http://www.csls.ca/ipm/ipm25.asp</u>

Bauer, Harald, Jan Viera, and Florian Weig, "Moore's Law: Repeal or Renewal," McKinsey & Company, December, 2013.

http://www.mckinsey.com/Insights/High\_Tech\_Telecoms\_Internet/Moores\_law\_Repeal\_or\_rene wal?cid=other-eml-alt-mip-mck-oth-1312

Berndt, Ernst R., and Zvi Griliches, "Price Indexes for Microcomputers: An Exploratory Study," in Murray F. Foss, Marilyn E. Manser, and Allan H. Young, eds., *Price Measurements and Their Uses*, 63–93, University of Chicago Press and National Bureau of Economic Research, Studies in Income and Wealth, vol. 57, 1993. <u>http://www.nber.org/chapters/c7798</u>

Brynjolfsson, Erik, and Andrew McAfee, *The Second Machine Age*, W.W. Norton and Company, 2014.

Byrne, David M., Stephen D. Oliner, and Daniel E. Sichel, "Is the Information Technology Revolution Over?" *International Productivity Monitor*, 25, 20–36, 2013. <u>http://www.csls.ca/ipm/ipm25.asp</u>

Chwelos, Paul, "Hedonic Approaches to Measuring Price and Quality Change in Personal Computer Systems," Ph.D. thesis, University of British Columbia, 2000. <u>https://circle.ubc.ca/handle/2429/11401</u>

\_\_\_\_\_, "Approaches to Performance Measurement in Hedonic Analysis: Price Indexes for Laptop Computers in the 1990's, *Economics of Innovation and New Technology*, 12(3), 199–224, 2003.

Cole, Rosanne, Y.C. Chen, Joan A. Barquin-Stolleman, Ellen Dulberger, Nurhan Halvacian, and James H. Hodge, "Quality-Adjusted Price Indexes for Computer Processors and Selected Peripheral Equipment," *Survey of Current Business*, 66(1), 41–50, 1986.

Cowen, Tyler, *The Great Stagnation: How America Ate All the Long-Hanging Fruit of Modern History, Got Sick, and Will (Eventually) Feel Better Again, Dutton, 2011*

Erickson, Tim and Ariel Pakes, "An Experimental Component Index for the CPI: From Annual Computer Data to Monthly Data on Other Goods," *American Economic Review* 101 (August), 1707-1738, 2011.

Fernald, John G., "Productivity and Potential Output Before, During, and After the Great Recession," in *NBER Macroeconomics Annual*, ed. by Jonathan Parker and Michael Woodford, 2014.

Flamm, Kenneth, "Measurement of DRAM Prices: Technology and Market Structure," in Murray F. Foss, Marilyn E. Manser, and Allan H. Young, eds., *Price Measurements and Their Uses*, 157-97, University of Chicago Press and National Bureau of Economic Research, Studies in Income and Wealth, vol. 57, 1993. <u>http://www.nber.org/chapters/c7802.pdf</u>

, "The Microeconomics of Microprocessor Innovation," manuscript, University of Texas, Austin, 2007.

Gordon, Robert J., "Is U.S. Economic Growth Over? Faltering Innovation Confronts the Six Headwinds," NBER Working Paper 18315, August, 2012.

, "The Demise of U.S. Economic Growth: Restatement, Rebuttal, and Reflections." NBER Working Paper 19895, February, 2014(a).

, "A New Method of Estimating Potential Real GDP Growth: Implications for the Labor Market and the Debt/GDP Ratio," NBER Working Paper 20423, August, 2014(b).

Grimm, Bruce T., "Price Indexes for Selected Semiconductors, 1974-96," *Survey of Current Business*, 78(2), 8–24, 1998.

Hall, Robert E. "Quantifying the Lasting Harm to the U.S. Economy from the Financial Crisis," in *NBER Macroeconomics Annual*, ed. by Jonathan Parker and Michael Woodford, 2014.

Hamilton Project, "The Future of Work in the Age of the Machine," Brookings Institution, February 19, 2015.

http://www.hamiltonproject.org/files/downloads\_and\_links/2015\_02\_24\_THP\_Future\_of\_Work in\_Machine\_Age\_transcript\_unedited.pdf.

Hennessy, John L. and David A. Patterson, *Computer Architecture: A Quantitative Approach* (5<sup>th</sup> ed.), Elsevier Science, 2012.

Holdway, Mike, "An Alternative Methodology: Valuing Quality Change for Microprocessors in the PPI," manuscript, 2001. <u>http://www.bea.gov/papers/pdf/mpuvqa.pdf</u>

Intel Corporation, "Excerpts from a Conversation with Gordon Moore: Moore's Law," 2005. http://large.stanford.edu/courses/2012/ph250/lee1/docs/Excepts\_A\_Conversation\_with\_Gordon\_ Moore.pdf

Jorgenson, Dale W., "Information Technology and the U.S. Economy," *American Economic Review*, 91(1), 1–32, 2001.

Jorgenson, Dale W., Mun S. Ho, and Jon D. Samuels, "What Will Revive U.S. Economic Growth? Lessons from a Prototype Industry-Level Production Account for the United States," *Journal of Policy Modeling*, 36, 674-91, 2014.

Moore, Gordon E. "Cramming More Components onto Integrated Circuits." *Electronics*, 38(8), April 19, 1965.

Nosko, Christopher, "Competition and Quality Choice in the CPU Market," manuscript, Harvard University, 2010. <u>http://faculty.chicagobooth.edu/chris.nosko/research/nosko\_cpu.pdf</u>

Pakes, Ariel, "A Reconsideration of Hedonic Price Indexes with an Application to PC's," *American Economic Review*, 93(5), 1578–96, 2003.

Pillai, Unni, "A Model of Technological Progress in the Microprocessor Industry," *Journal of Industrial Economics*, 61(4), 877–912, 2013.

Shenoy, Sunil R, and Akhilesh Daniel, "Intel Architecture and Silicon Cadence: The Catalyst for Industry Innovation," *Technology at Intel Magazine*, 2006.

State of New York v. Intel Corporation, No. 1:09-cv-00827 (D. Del), Nov. 4, 2009.

Sun, Sophie, "What are We Paying For? A Quality-adjusted Price Index for Laptop Microprocessors," Wellesley College senior thesis, 2014.

Triplett, Jack E., "Price and Technological Change in a Capital Good: A Survey of Research on Computers," in Dale W. Jorgenson and Ralph Landau, eds., *Technology and Capital Formation*, 127-213, MIT Press, Cambridge, MA, 1989.

\_\_\_\_\_\_, "Handbook on Hedonic Indexes and Quality Adjustments: Special Application to Information Technology Products," Organisation for Economic Co-operation and Development, Paris and Washington, D.C., 2006. http://browse.oecdbookshop.org/oecd/pdfs/free/9306081e.pdf

| Industry Fro | ontier | Inte      | Intel MPU Chips |  |  |

|--------------|--------|-----------|-----------------|--|--|

| Period Years |        | Period    | l Years         |  |  |

| 1969-1993    | 3.0    | 1971-1994 | 2.9             |  |  |

| 1993-2012    | 2.1    | 1994-2012 | 1.9             |  |  |

| 1993-2003    | 1.9    | 1994-200  | 1.9             |  |  |

| 2003-2012    | 2.3    | 2004-201  | 2 2.0           |  |  |

Table 1. Semiconductor Technology Cycles

(Years needed for 30 percent reduction in linear scaling)

Source. Byrne, Oliner, and Sichel (2013).

# Table 2. Sample Characteristics: Is Sample Selection a Problem?

|                                      | 2000-04 | 2005-08 | 2009-13 |  |

|--------------------------------------|---------|---------|---------|--|

| Number of Intel desktop MPU models   |         |         |         |  |

| With SPEC available                  | 38      | 60      | 86      |  |

| No SPEC available                    | 47      | 45      | 97      |  |

| Universe                             | 85      | 105     | 183     |  |

| Entry price (\$)                     |         |         |         |  |

| With SPEC available                  | 512     | 416     | 243     |  |

| No SPEC available                    | 181     | 197     | 168     |  |

| Clock speed (ghz)                    |         |         |         |  |

| With SPEC available                  | 2.07    | 2.86    | 3.00    |  |

| No SPEC available                    | 1.95    | 2.80    | 2.76    |  |

| Number of cores                      |         |         |         |  |

| With SPEC available                  | 1.0     | 2.25    | 3.09    |  |

| No SPEC available                    | 1.0     | 1.44    | 2.76    |  |

| Maximum thermal design power (watts) |         |         |         |  |

| With SPEC available                  | 60.3    | 92.3    | 75.1    |  |

| No SPEC available                    | 55.2    | 78.8    | 59.1    |  |

| Lithography size (nanometers)        |         |         |         |  |

| With SPEC available                  | 147.9   | 65.2    | 31.3    |  |

| No SPEC available                    | 134.7   | 73.9    | 30.9    |  |

# Panel A: Number of Intel models, characteristics, and price levels, by year of introduction

## Panel B: Price changes (percent, average annual rate)

|                                                                                                                | 2000-04           | 2004-08           | 2008-13        | 2000-13           |

|----------------------------------------------------------------------------------------------------------------|-------------------|-------------------|----------------|-------------------|

| PPI-like matched-model price index<br>(Intel MPUs)<br>With SPEC available<br>No SPEC available<br>All desktops | -56<br>-48<br>-53 | -19<br>-24<br>-22 | -7<br>-6<br>-6 | -29<br>-26<br>-28 |

| РРІ                                                                                                            | -48               | -29               | -8             | -28               |

Source. Authors' calculations based on data from System Performance Evaluation Corporation, Intel price lists, and data from http://ark.intel.com.

# Table 3. Regression Results for 2000-06

|                         | 2000-01       | 2001-02 | 2002-03 | 2003-04 | 2004-05 | 2005-06 |

|-------------------------|---------------|---------|---------|---------|---------|---------|

| V                       | 895**         | 363     | 995**   | 929*    | 263     | 819*    |

| Year dummy              | (.177) (.209) | (.287)  | (.281)  | (.277)  | (.311)  |         |

|                         | .63*          | 1.12**  | 2.98**  | 3.99**  | 4.39**  | 2.95**  |

| ln Performance          | (.27)         | (.29)   | (.69)   | (.80)   | (1.01)  | (.74)   |

| Number of Obs.          | 20            | 18      | 14      | 11      | 23      | 28      |

| Adjusted R <sup>2</sup> | .56           | .48     | .56     | .70     | .44     | .34     |

# **Panel A: Introduction period only**

# Panel B: Full sample

|                         | 2000-01 | 2001-02 | 2002-03 | 2003-04 | 2004-05 | 2005-06 |

|-------------------------|---------|---------|---------|---------|---------|---------|

| V                       | 875**   | 318**   | 403**   | 489**   | 436**   | 494**   |

| Year dummy              | (.097)  | (.072)  | (.090)  | (.115)  | (.124)  | (.092)  |

| In Performance          | 1.05**  | .87**   | 1.13**  | 2.81**  | 3.15**  | 2.52**  |

|                         | (.15)   | (.09)   | (.12)   | (.26)   | (.35)   | (.28)   |

| Number of Obs.          | 100     | 111     | 94      | 78      | 107     | 157     |

| Adjusted R <sup>2</sup> | .46     | .44     | .47     | .62     | .43     | .35     |

Note: The dependent variable is ln(MPU price); the regression includes a constant, not shown above. Standard errors are in parentheses. \* and \*\* indicate significance at the 5% and 1% levels, respectively.

# Table 4. Regression Results for 2006-13

|                         | 2006-07 | 2007-08 | 2008-09 | 2009-10 | 2010-11  | 2011-12 | 2012-13 |

|-------------------------|---------|---------|---------|---------|----------|---------|---------|

| Vo an deman             | 726     | 784*    | 754     | 335     | -1.229** | 481**   | 533**   |

| Year dummy              | (.388)  | (.226)  | (.369)  | (.244)  | (.226)   | (.110)  | (.091)  |

| In Doutomanao           | 1.87*   | 2.39**  | 2.86**  | 2.79**  | 3.31**   | 2.88**  | 2.88**  |

| ln Performance          | (.76)   | (.82)   | (.70)   | (.65)   | (.50)    | (.31)   | (.20)   |

| Observations            | 24      | 26      | 27      | 25      | 35       | 50      | 31      |

| Adjusted R <sup>2</sup> | .16     | .28     | .41     | .41     | .58      | .65     | .87     |

# Panel A: Introduction period only

# Panel B: Full sample

|                         | 2006-07 | 2007-08 | 2008-09 | 2009-10 | 2010-11 | 2011-12 | 2012-13 |

|-------------------------|---------|---------|---------|---------|---------|---------|---------|

| Vo an dumme             | 743**   | 533**   | 555**   | 177**   | 436**   | 469**   | 203**   |

| Year dummy              | (.140)  | (.112)  | (.082)  | (.064)  | (.069)  | (.068)  | (.054)  |

| In Daufamu an aa        | 2.22**  | 2.19**  | 1.73**  | 1.53**  | 1.14**  | 1.21**  | 2.98**  |

| ln Performance          | (.28)   | (.22)   | (.14)   | (.09)   | (.09)   | (.11)   | (.16)   |

| Observations            | 88      | 141     | 187     | 217     | 281     | 294     | 214     |

| Adjusted R <sup>2</sup> | .41     | .41     | .46     | .57     | .35     | .29     | .63     |

Note: The dependent variable is ln(MPU price); the regression includes a constant, not shown above. Standard errors are in parentheses. \* and \*\* indicate significance at the 5% and 1% levels, respectively.

#### Table 5. Rates of change in MPU prices<sup>1</sup>

(Average annual percent change over periods shown)

|                                    | 2000-04 | 2004-08 | 2008-13 | 2000-13 |

|------------------------------------|---------|---------|---------|---------|

| Hedonic, SPEC performance          |         |         |         |         |

| Introduction period                | -52     | -37     | -43     | -44     |

| Full sample                        | -40     | -33     | -22     | -31     |

|                                    |         |         |         |         |

| Hedonic, chip characteristics      |         |         |         |         |

| Introduction period                | -43     | -1      | -21     | -23     |

| Full sample                        | -39     | -16     | -13     | -23     |

|                                    |         |         |         |         |

| Federal Reserve Board <sup>2</sup> | -51     | -29     | -31     | -38     |

|                                    |         |         |         |         |

| PPI                                | -48     | -29     | -8      | -28     |

1. The results for the hedonic regressions have been bias-corrected for the conversion from the natural log of price to the price level. See the text for details.